Hsinchu, Taiwan and Oxford, UK , Dec. 03, 2020 (GLOBE NEWSWIRE) -- Andes Technology Corp., a leading supplier of performance-efficient and extensible 32/64-bit RISC-V CPU cores and a Founding Premier member of the RISC-V International Association, and Imperas Software Ltd., a leader in high-performance software simulation and virtual platforms, announced today to extend their cooperation to the versatile Andes Custom Extension™ (ACE) and Imperas’ fast simulators. The joint work enables SoC design teams using the ACE framework to co-design hardware and software so that full software development can start before the silicon is available.

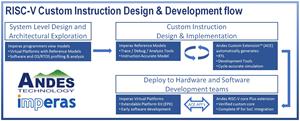

Under the ACE framework, SoC designers can easily and efficiently define new instructions on the Andes RISC-V processor core to speed up target applications by writing ACE scripts for instruction semantics and concise Verilog for instruction execution RTL. Taking them as inputs, the powerful tool COPILOT (Custom-OPtimized Instruction deveLOpment Tools) automatically generates all required components to extend the existing Andes processor package, including the processor RTL, the compilation tools, the debugger and the cycle-accurate simulator, to support the new instructions.

While SoC architects and logic designers focus on accelerating the most time critical parts of their applications, software engineers need to ensure the functionality and robustness of the whole software stack and put in new features at the same time. Before the SoC silicon is available for full-speed development, a fast simulator allows software engineers to jump-start the coding, debugging and testing of their applications without depending on the schedule of the hardware development. By taking the extended simulation shared library generated by the COPILOT, the Imperas simulators can automatically recognize the new instructions and simulate their functionality just like a hand-customized simulator. With a fast simulator and the associated tools, software engineers can start full development and even provide feedbacks to hardware designers.

“All Andes RISC-V CPU cores are extensible. ACE empowers SoC designers to easily add custom instructions on top of our highly efficient cores to fulfill domain-specific acceleration and bring their SoC performance to the next level,” says Dr. Charlie Su, Andes Technology CTO and EVP. “Our RISC-V CPU cores are supported by the Imperas simulators already. We are excited to extend our cooperation to enable ACE users to use the Imperas fast simulators so that software engineers can also be engaged with the full development cycle and from the early stage.”

“The flexibility of RISC-V with custom extensions, while compliant with the software ecosystem, offers new degrees of freedom for system architects,” says Simon Davidmann, CEO at Imperas Software Ltd. “Rapid software architectural exploration with virtual platforms complements the ACE hardware implementation flow, plus the resulting platforms offer virtual development boards well before silicon is available. Andes and Imperas working together are helping customers and partners innovate hardware flexibility at the speed of software development.”

The cooperation enhances the ACE solution with the Imperas fast simulators and virtual platforms. SoC design teams using the ACE framework for Andes RISC-V processor cores can define custom instructions and have all the required components generated automatically in no time on their desktops by the COPILOT tool. They include extended components for the processor RTL, the compilation tools, the debugger, the cycle-accurate simulator as well as the Imperas fast functional simulators.

About Imperas

Imperas is revolutionizing the development of embedded software and systems and is the leading provider of RISC-V processor models and virtual prototype solutions. Imperas, along with Open Virtual Platforms (OVP), promotes open-source model availability for a spectrum of processors, IP vendors, CPU architectures, system IP and reference platform models of processors and systems ranging from simple single core bare metal platforms to full heterogeneous multi-core systems booting SMP Linux. All models are available from Imperas at

www.imperas.com and the Open Virtual Platforms (OVP) website at

www.ovpworld.org.

About Andes

Andes Technology Corporation is a world class creator of innovative high-performance/low-power 32/64-bit processor cores and associated development environment that serves the rapidly growing global market for embedded system applications. As a Founding Premier member of RISC-V International, Andes is the first mainstream CPU vendor that has adopted the RISC-V as the base of its fifth-generation architecture, the AndeStar™ V5. To meet the demanding requirements of today's electronic devices, Andes delivers highly configurable, extensible and performance-efficient CPU cores with full-featured integrated development environment and comprehensive software/hardware solutions to help customers innovate their SoC in a shorter time to market. Since 2018, the yearly volume of SoCs Embedded with Andes CPUs has surpassed the 1-billion mark. Andes Technology's comprehensive RISC-V CPU families range the compact 25-series, the advanced 27-series to the high-performance superscalar 45-series.

For more information, please visit

http://www.andestech.com

Attachment

Hsiao-Ling Lin E-mail: hllin@andestech.com Web: www.andestech.com