The Catapult® and PowerPro® family of products enables ASIC, SOC and FPGA designers to quickly create fully-verified, power-optimized RTL for downstream synthesis and physical design.

Using the Catapult High-Level Synthesis Platform, designers have the option of using C, SystemC or C++ as a design entry language to dramatically shorten the design and verification cycle by producing correct-by-construction, error-free, power-optimized RTL.

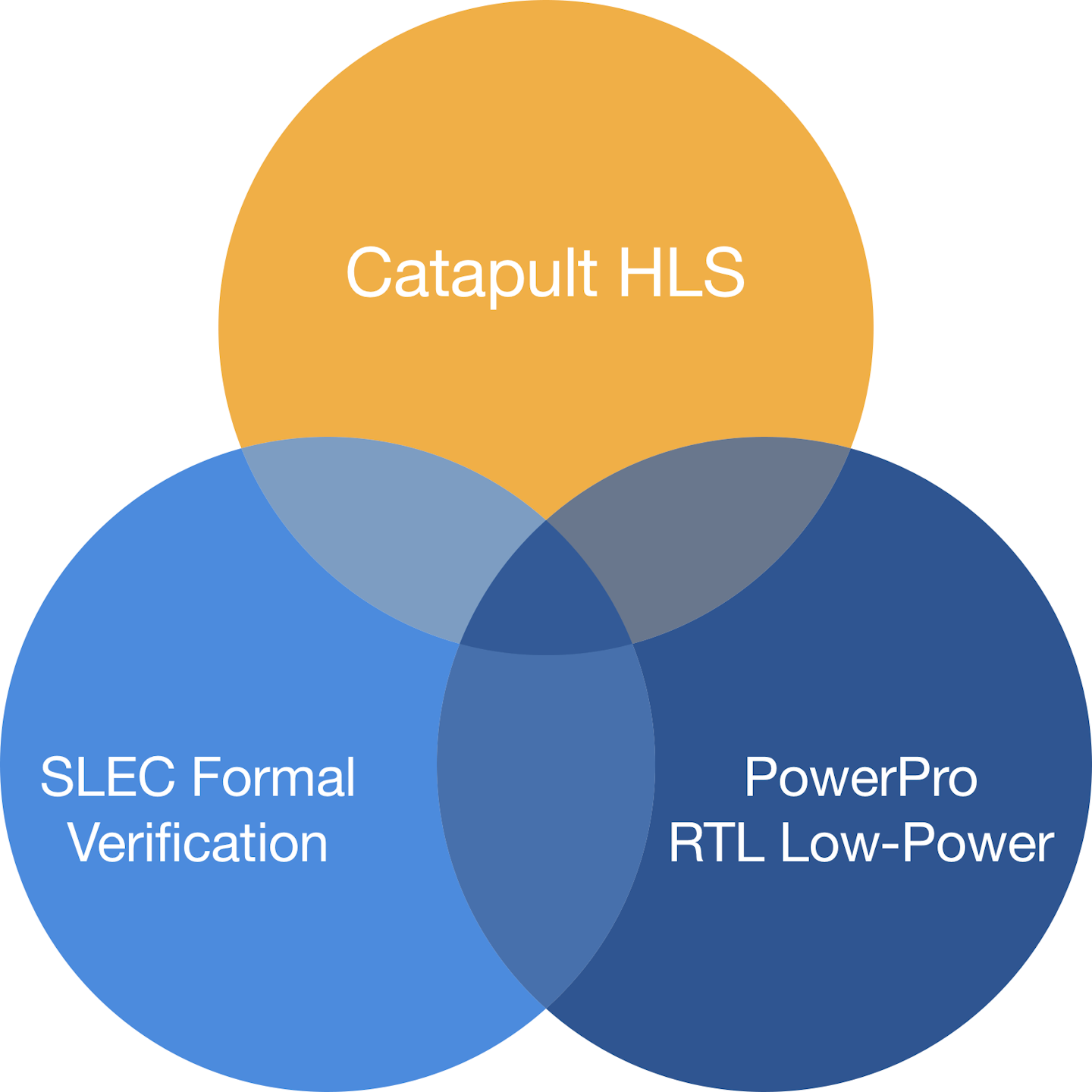

The PowerPro RTL Low-Power Platform enables designers to analyze both static and dynamic RTL power usage and either automatically or manually create power-optimized RTL that includes memory and leakage power optimization. The SLEC® formal verification products work with both platforms to formally verify the RTL without the need for time-consuming simulation and complex testbenches. All products are tightly integrated, to enable dramatic reduction in time to market and power usage.

Technologies

Catapult High-Level Synthesis

Lets designers use industry-standard ANSI C++ or SystemC to describe functional intent at the ESL level. From these high-level descriptions, the HLS products automatically generate production-quality RTL which dramatically shortens both design and verification time in hardware design flows.

PowerPro RTL Low-Power

The PowerPro RTL Low-Power platform provides a complete solution to accurately measure, interactively explore and thoroughly optimize power during the RTL development cycle. Deep Sequential Analysis of design redundancies, aided by physical-aware power-analysis, provides the best power optimization possible for any design.