Latest DSP quadruples neural network performance capability compared to previous-generation Vision DSP

SAN JOSE, Calif., May 2, 2016 — (PRNewswire) — Cadence Design Systems, Inc. (NASDAQ: CDNS) today announced the new Cadence® Tensilica® Vision P6 digital signal processor (DSP), Cadence's highest-performing vision/imaging processor, which extends the Tensilica product portfolio further into the fast-growing vision/deep learning applications areas. New instructions, increased math throughput and other enhancements set a new standard in imaging and computer vision benchmarks, increasing performance by up to 4X compared to the Tensilica Vision P5 DSP.

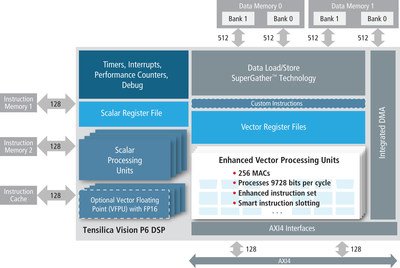

The Tensilica Vision P6 DSP quadruples multiply-accumulate (MAC) performance compared to the previous generation Vision P5 DSP, targeting convolutional neural network (CNN) applications which are dominated by available MAC performance. Compared to commercially available GPUs, the Tensilica Vision P6 DSP can achieve twice the frame rate at much lower power consumption on a typical neural network implementation. For a wide range of other key vision functions, such as convolution, FIR filters and matrix multiplication, the Tensilica Vision P6 DSP increases performance by up to 4X by utilizing its improved 8-bit and 16-bit arithmetic, making it an ideally suited DSP for CNN applications. In addition, the Tensilica Vision P6 implements on-the-fly data compression to sharply reduce memory footprint and bandwidth requirements for demanding "fully connected" neural network layers.

The Tensilica Vision P6 DSP builds on the momentum of the market-leading Vision P5 DSP, which has already been designed-in by two of the leading mobile phone application processor vendors. Compatible with the Vision P5 DSP, this newest vision DSP offers an optional 32-way SIMD vector floating-point unit that includes the IEEE half precision standard (FP16). Floating-point performance capability is double that of the Vision P5 DSP, enabling easy use of existing floating-point neural network implementations.

The advances in the Tensilica Vision P6 DSP further improve the ease of software development and porting, with comprehensive support for integer, fixed-point and floating-point data types and an advanced toolchain with a proven auto-vectorizing C compiler. The software environment also features complete support for standard OpenCV and OpenVX libraries, enabling fast, high-level migration of existing imaging/vision applications with support of over 1000 library functions. Early customer engagements on the Tensilica Vision P6 DSP are expected to begin in late June. For more information on the Tensilica Vision P6 DSP, contact your Cadence representative or visit http://www.cadence.com/news/TensilicaVisionP6.

"Cadence is investing heavily on advanced vision and deep learning," said Chris Rowen, CTO for the IP Group at Cadence. "We are devoting intense efforts to discovering improved structures and training for neural networks, providing rich software environments for fast application development and offering breakthrough vision DSP architectures for embedded vision and learning deployment. The Tensilica Vision P6 design is the direct result of this investment and significantly raises the bar in both vision efficiency and scalability."

"We have been working closely with Cadence to develop CNN-based vision applications. Features such as wide vector SIMD processing, VLIW instructions, and fast histogram and scatter/gather intrinsics make it an ideal platform for demanding CNN algorithms," said A. G. K. Karunakaran, president and CEO of Multicoreware. "The Tensilica Vision DSP's performance characteristics, combined with its highly tuned image processing libraries and robust development environment, enabled a power-efficient implementation of our algorithms and shortened our development cycle. We are excited to continue working with Cadence on their next-generation Vision P6 DSP."

"Devices that are more aware of the world around them are more capable, more autonomous, safer and easier to use," said Jeff Bier, founder of the Embedded Vision Alliance. "By enabling widespread deployment of deep learning and computer vision, processors like the Tensilica Vision P6 DSP are making the promise of more intelligent devices a reality."

The Tensilica Vision P6 DSP is based on the Cadence Tensilica Xtensa® architecture, and combines flexible hardware choices with a library of vision/imaging DSP functions and numerous vision/imaging applications from our established ecosystem partners. It also shares the comprehensive Tensilica partner ecosystem for other applications software, emulation and probes, silicon and services and much more. The Xtensa architecture is one of the most popular licensable processor architecture, shipping products spanning from sensors to supercomputers.

About Cadence

Cadence enables global electronic design innovation and plays an essential role in the creation of today's integrated circuits and electronics. Customers use Cadence software, hardware, IP and services to design and verify advanced semiconductors, consumer electronics, networking and telecommunications equipment, and computer systems. The company is headquartered in San Jose, Calif., with sales offices, design centers and research facilities around the world to serve the global electronics industry. More information about the company, its products and its services is available at

http://www.cadence.com.

This press release contains certain forward-looking statements that are based on our current expectations and involve numerous risks and uncertainties that may cause these forward-looking statements to be inaccurate. Risks that may cause these forward-looking statements to be inaccurate include, among others, the risks detailed from time-to-time in our U.S. Securities and Exchange Commission filings and reports, including, but not limited to, our most recent quarterly report on Form 10-Q and our annual report on Form 10-K. We do not intend to update the information contained in this press release.

© 2016 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, Tensilica, and Xtensa are registered trademarks of Cadence Design Systems, Inc. in the United States and other countries. All other trademarks or registered trademarks are those of their respective holders.

For more information, please contact:

Cadence Newsroom

408-944-7039

Email Contact

Photo - http://photos.prnewswire.com/prnh/20160428/361490

Logo - http://photos.prnewswire.com/prnh/20140102/SF39436LOGO

To view the original version on PR Newswire, visit: http://www.prnewswire.com/news-releases/cadence-announces-new-tensilica-vision-p6-dsp-targeting-embedded-neural-network-applications-300259928.html

SOURCE Cadence Design Systems, Inc.

| Contact: |

| Cadence Design Systems, Inc.

Web: http://www.cadence.com |