SonicsStudio® 8.0 Features Major Enhancements to the Director User Interface, Studio Generation Tools, and Automated Development Flow

MILPITAS, Calif., June 8, 2015 — (PRNewswire) — Sonics, Inc., the world's foremost supplier of on-chip network (NoC) technologies and services, today introduced SonicsStudio 8.0, the latest release of its next-generation system-on-chip (SoC) development environment that includes improvements for both designer productivity and power analysis. In Release 8.0, Sonics has added major new features to all three areas of SonicsStudio: the Director user interface, the underlying SonicsStudio generation tools, and the automated development flows for stimulus generation, simulation, synthesis, and performance/power analysis.

"No other SoC development environment comes close to SonicsStudio for ease-of-use in graphical design capture with NoCs, accuracy in dynamic power analysis, and seamless, front-to-back design flow integration," said Drew Wingard, CTO of Sonics. "Release 8.0 of SonicsStudio incorporates many new capabilities our NoC customers requested to improve productivity using the environment and produce better quality of results in silicon."

SonicsStudio Director User Interface

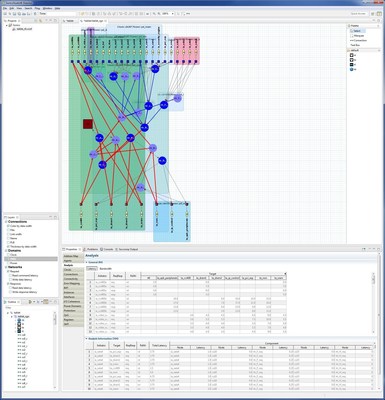

The focus of Release 8.0 is providing additional information in Director's graphical views that enable designers to see at a glance key characteristics of their network, for example:

- Colored backgrounds identify the clocking or power domain for component groups

- Tick marks identify all structural and optional re-timing stages with annotation for asynchronous or mesochronous clock crossing elements

- Color and line widths indicate internal link widths

These improvements to the Director user interface make it much easier to inspect and capture the design. They enable designers to graphically view the clock and power domains and the partitioning. Designers can easily see the width of all the individual links between the NoC routers and agents to quickly perform a visual audit. The re-timing view displays all of the re-timing stages in the different components of the system. If designers are interested in the latency between two components, they can quickly view the entire path and count the number of re-timing stages very directly and intuitively.

SonicsStudio Generation Tools

Release 8.0 incorporates substantial improvements for designers implementing power-optimized SoCs. For example:

- The soccomp netlist generator adds the capability to bundle all of the Sonics IP in a given power domain into a unique RTL hierarchy, splitting a network like SonicsGN into parts at power domain crossings. This greatly simplifies the top level integration challenge where physical design flows require RTL hierarchies that match power domain partitioning.

- The socmap constraint generator now outputs complete power intent information in either IEEE 1801 UPF or CPF forms. This allows clock and power domain partitioning decisions made during design capture in Director to be seamlessly transferred to the rest of the design process.

Automated Development Flow

Release 8.0 provides more design flow automation for performance and power analysis. On the performance analysis side, a new parser imports the results from RTL or third-party ESL simulators into the Director database format with support for complete, multi-hop transaction tracing. This improves analysis and debug performance for designers whether they are using SystemC, RTL or other simulation approaches.

On the power side, the development flow now supports automatic gate-level simulation of collections of Sonics IP using the same traffic patterns from performance simulations together with the extraction of dynamic power results based on the switching activity from these simulations. This makes accurate, push-button dynamic power analysis available much earlier in the design process - early enough to use while considering power partitioning decisions. It is particularly important to use realistic traces when estimating the power of on-chip networks because their distributed nature and asymmetric communication patterns make uniform activity factor-based analysis almost meaningless.

The development flow also includes template generation to use the UPF or CPF power intent outputs from socmap in later stages of the customer design flow. This eases integration of SonicsStudio with industry-standard tooling and improves customer usability.

Availability

SonicsStudio 8.0 is available to early access customers now with general availability in July. For more information on SonicsStudio 8.0, contact your Sonics sales representative.

About Sonics, Inc.

Sonics, Inc. (Milpitas, Calif.) is the trusted global leader in on-chip network (NoC) technologies used by the industry's top semiconductor and electronics product companies. Sonics was the first company to develop and commercialize NoCs, accelerating volume production of complex systems-on-chip (SoC) that contain multiple processor cores. Our comprehensive NoC portfolio delivers the communication performance required by today's most advanced consumer digital, communications and information technology devices. Sonics' NoCs are integral to the success of SoC design platforms that innovators such as Broadcom®, Intel®, Marvell®, MediaTek, and Microchip® rely on to meet their most demanding SoC integration and time-to-market requirements. We are a catalyst for design methodology change and actively drive industry conversation on the

Agile IC LinkedIn group. Sonics' holds approximately 150 patent properties supporting customer products that have shipped more than four billion SoCs. For more information, visit

sonicsinc.com, and follow us on Twitter at

twitter.com/sonicsinc.

Contact: Erica Harbison

McClenahan Bruer

Email Contact | 503.546.1013

Photo - http://photos.prnewswire.com/prnh/20150605/221242

To view the original version on PR Newswire, visit: http://www.prnewswire.com/news-releases/sonics-upgrades-designer-productivity-and-power-analysis-capabilities-in-next-generation-soc-development-environment-300095109.html

SOURCE Sonics, Inc.

| Contact: |

| Sonics, Inc.

Web: http://www.sonicsinc.com |